# Deanship of Graduate Studies Al-Quds University

# A Non-blocking Interconnection Network-Shared Cache Organization for Multi-core Processors

**Allam Rebhi Mohammad Abumwais**

**M.Sc Thesis**

Jerusalem-Palestine

## A Non-blocking Interconnection Network-Shared Cache Organization for Multi-core Processors

### **Prepared By:**

#### Allam Rebhi Mohammad AbuMwais

B.Sc.: Computer Engineering, 2013, Palestine

Alquds University, Palestine

Supervisor: Dr. Abdualkareem Ayyad

A thesis submitted in partial fulfilment of the requirements for the degree of Master of Electronic and Computer Engineering/Department of Electronic and Computer Engineering/ Faculty of Engineering/ Graduate Studies

Jerusalem-Palestine

1434-2013

### Al-Quds University

### Deanship of Graduate Studies

### Master of Electronics and Computer Engineering

### Thesis Approval

### A Non-blocking Interconnection Network-Shared Cache Organization for Multi-core Processors

Prepared By: Allam Rebhi Mohammad AbuMwais

Registration No: 21011963

Supervisor: Dr. Abdulkareem Ayyad

Master thesis submitted and accepted, Date: 00/00/2013

The name and signatures of examining committee members are as follows:

| 1- Head of committee | Dr. Abdulkareem Ayyad | Signature: |

|----------------------|-----------------------|------------|

| 2- Internal Examiner | Dr.                   | Signature: |

| 3- External Examiner | Dr.                   | Signature: |

Jerusalem-Palestine

**Declaration:**

I certify that this thesis submitted for the degree of Master, is the result of

my own research, except where otherwise acknowledged, and that this

study (or any part of the same) has not been submitted for a higher

degree to any other university or institution.

Signed: .....

Allam Rebhi Mohammad Abu Mwais

Date: 28/9/2013

i

# Acknowledgments

I thank God for everything.

I would like to express my deepest appreciation to my family especially my parents, for the endless care they have provided me, advices, support and patience.

Special thanks goes out to my supervisor, Dr. Abdulkareem Ayyad, whose give me more knowledge and skills in the computer architecture field. Also, his guidance helped me throughout this research and the writing of this thesis.

My deep gratitude goes to all my friends, especially at Al-Quds University.

I would like to thank all those who helped me during the period of my study and give me motivation and encouragement.

#### **Abstract**

In modern on-chip multi-core processors and multiprocessor systems, the communication between the processor cores and the shared memory modules of the system, (here in after, the terms 'shared memory' and 'shared cache' can be used interchangeably), suffers from a bottleneck problem. In the best interconnection network, the crossbar switch, when two or more cores make a request to access the same shared cache module, only one request will be accepted and the other requests have to be honoured in a sequence decided by the arbiter of that module. This increases the latency of the shared variable access. This considerably slows the performance of the cores in executing the program threads and hence, the whole execution process.

In our proposed model for multi-core processor architecture, we have redesigned the shared cache modules and the interconnection network organization. This resulted in a Multi-port Content Addressable Memory (MPCAM) and the bottleneck has been totally eliminated. All the cores of the system can write to and read from this memory simultaneously. The shared variable communication process through this memory, by itself guarantees the snooping cache coherence process automatically. It worth noting that the cache coherence process increases the communication overhead in the current systems. In this organization, there is no queuing, no arbitration, and hence no additional latency. A latency of less than or equal five nanoseconds per shared variable access has been achieved. The simulation results of the MPCAM as part of a multi-core architecture have shown high bandwidth, and negligible cache miss ratio, negligible cache coherence and synchronization overhead as compared to the eight core AMD architecture. At the end of this work, the authors have proposed a linear scalable scheme which expands the system to include large number of cores with

linear growing cost and minimum fixed latency of 1.5t, where t is the MPCAM access time.

**Keywords:** Multi-core, Multi-threading, Micro-threading, Content Addressable Memory (CAM), Cache Coherence, shared Variables, Interconnection Network, Bottleneck, Contention, Arbitration.

# **Table of Contents**

| Declaration                                             | 1                              |

|---------------------------------------------------------|--------------------------------|

| Acknowledgments                                         | Error! Bookmark not defined.   |

| Abstract .                                              | iii                            |

| Table of Contents                                       | Error! Bookmark not defined.   |

| List of Figures                                         | Error! Bookmark not defined.ii |

| Chapter 1 Introduction                                  | 1                              |

| 1.1 Motivation                                          | 1                              |

| 1.2 Problem Specification and Justification             | 2                              |

| 1.3 Thesis Contribution                                 | 3                              |

| 1.4 Thesis Organization                                 | 3                              |

| Chapter 2 Background and Related Work                   | 5                              |

| 2.1 Current Approach                                    | 5                              |

| 2.1.1 Multiprocessors Systems                           | 5                              |

| 2.1.2 Multi-core System                                 | 6                              |

| 2.2 Alternate Approach                                  | 7                              |

| 2.2.1 Multi-core Processor Architecture                 | 7                              |

| 2.2.2 Multithreading and Micro-threading                | 10                             |

| 2.2.3 Valgrind Simulator Tool                           | 12                             |

| 2.3 Major Issues in Multi-core System                   | 13                             |

| 2.3.1 The Scheduling Policy for Multiprocessor.         | 13                             |

| 2.3.2 Communication among the Cores                     | 14                             |

| 2.3.3 Cache Coherence Issue                             | 15                             |

| 2.4 Interconnection Networks in Multi-core Architecture | ture17                         |

| 2.4.1 The Common Bus Networks                           | 17                             |

| 2.4.2 The Crossbar Switch Networks                      | 18                             |

| 2.4.3 The Multiple Bus Network                          | 20                             |

| 2.4.4 Multistage Interconnection Networks               | 21                             |

| 2.5 Network on Chip on Modern Multi-core System.        | 22                             |

| 2.6 Types of Cache Memory                               | 23                             |

| 2.6.1 Fully Associative                                 | 23                             |

| 2.6.2 Direct Mapped                                     | 24                             |

| 2.6.3 Set-Associative Mapping                           | 25                             |

| 2.7 Cache Events Classification                         | 25                             |

| 2.7.1 Cache-Hit and Cache-Miss                                             | 26      |

|----------------------------------------------------------------------------|---------|

| 2.8 Embedded Memory Unit Crossbars Interconnection Networks                | 27      |

| Chapter 3 The Design of New Crossbar Embedded DPCAM and Simulation Results | 28      |

| 3.1 Cache Memory in Multi-core System                                      | 28      |

| 3.2 The Design of Dual-Port CAM and Multi-Port CAM                         | 29      |

| 3.2.1 Single Port CAM                                                      | 30      |

| 3.2.2 Dual Port CAM                                                        | 31      |

| 3.2.3 Multi Port CAM                                                       | 34      |

| 3.3 The Crossbar Embedded DPCAM Architecture (The MPCAM)                   | 34      |

| 3.3.1 The Claims for Embedded DPCAM Networks                               | 35      |

| 3.3.2 The Mathematical Model of Crossbar Embedded DPCAM Network            | 36      |

| 3.3.3 Comparing Results Between Crossbar Embedded DPCAM and Normal Cr      | rossbar |

| Switch                                                                     | 37      |

| 3.4 Simulation Results of Crossbar Embedded DPCAM Circuit                  | 40      |

| 3.5 Area Estimations and Model Complexity                                  | 40      |

| Chapter 4 Simulation Results within Multi-Core System                      | 46      |

| 4.1 AMD Vs. Our Model Architecture                                         | 46      |

| 4.2 Results                                                                | 49      |

| 4.2.1 Benchmarking program                                                 | 49      |

| 4.2.2 Single thread testing (date) and (df) program                        | 50      |

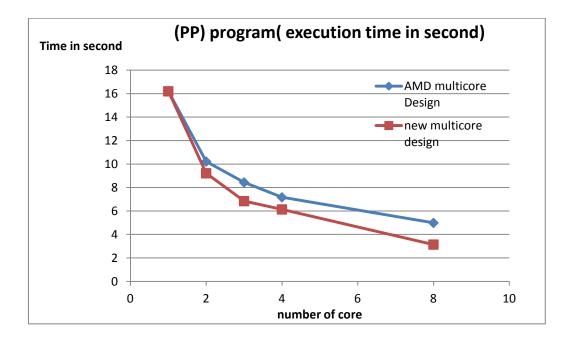

| 4.2.3 Multithreading Testing Performance Program (pp)                      | 51      |

| 4.2.4 Execution Time Using (pp)                                            | 51      |

| 4.3 Result Analysis                                                        | 53      |

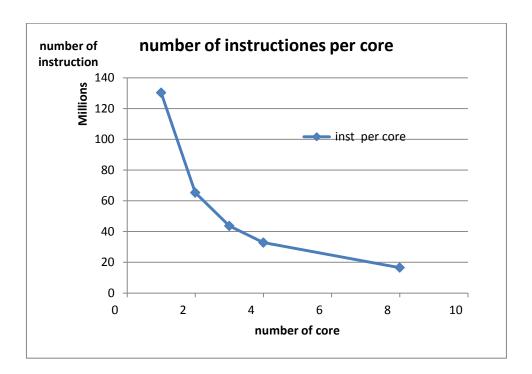

| 4.3.1 Number of Instructions per Core                                      | 53      |

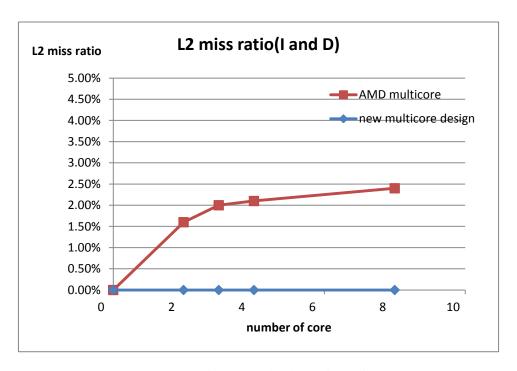

| 4.3.2 Cache L2 (Shared Variable) Misses                                    | 54      |

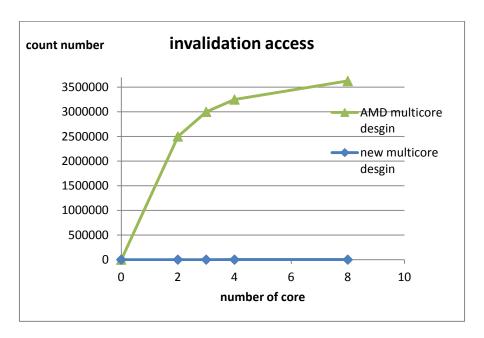

| 4.3.3 Number of Invalidation Access the Shared Variable                    | 55      |

| 4.3.4 Execution Time                                                       | 56      |

| Chapter 5 Conclusion and Future Work                                       | 58      |

| 5.1 Conclusion                                                             | 58      |

| 5.2 Future Work                                                            | 58      |

| Glossary                                                                   | 61      |

| Bibliography                                                               | 63      |

| Arabic Abstract                                                            | 70      |

| Annendices                                                                 | 71      |

# **List of Figures**

| Figure 2.1(a): A block Diagram of SSM System                            | 8  |

|-------------------------------------------------------------------------|----|

| Figure 2.1(b): Processing Elements (PEs)                                | 8  |

| Figure 2.2: A block Diagram of DSM System.                              | 9  |

| Figure 2.3: Multithreading Pipelining.                                  | 11 |

| Figure 2.4: The Cache Coherence Problem in Dual Core.                   | 15 |

| Figure 2.5: Common Bus Interconnection Networks.                        | 17 |

| Figure 2.6: Crossbar Switch Interconnection Networks.                   | 18 |

| Figure 2.7: Crossbar Switch with Arbitrator Interconnection Networks.   | 19 |

| Figure 2.8: Multiple Bus Interconnection Networks.                      | 20 |

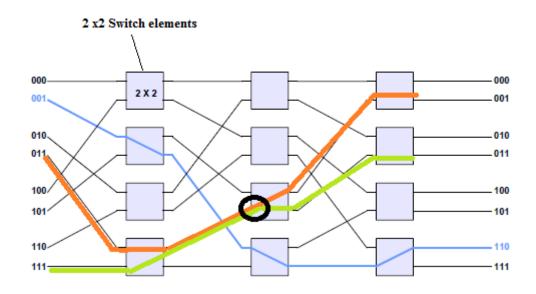

| Figure 2.9: Multistage Interconnections (MIN) with 2 x2 Switch Elements | 22 |

| Figure 2.10: The T1 Sun Multi-core Architecture                         | 23 |

| Figure 2.11: The Intel I7 Multi-core Architecture                       | 23 |

| Figure 2.12: Fully Associative Cache Memory                             | 24 |

| Figure 2.13: Set Associative Cache Memory                               | 25 |

| Figure 3.1: AMD Multi-core Cache Leve.                                  | 29 |

| Figure 3.2: Single Port CAM Design.                                     | 31 |

| Figure 3.3: The Dual Port CAM Design                                    | 32 |

| Figure 3.4: The Multi-port Content Addressable Memory                   | 34 |

| Figure 3.5: Bandwidth Function with(r=0.8)                              | 38 |

| Figure 3.6: Bandwidth Function with(r=0.5)                              | 38 |

| Figure 3.7: Bandwidth Function at Broadcast Situation(r=0.5)            | 39 |

| Figure 3.8: Crossbar Embedded DPCAM Functional Simulation               | 41 |

| Figure 3.9: Crossbar Embedded DPCAM Timing 1 Simulation                 | 42 |

| Figure 3.10: Crossbar Embedded DPCAM Timing 2 Simulation                | 42 |

| Figure 3.11: Crossbar Embedded DPCAM Timing 3 Simulation                | 43 |

| Figure 3.12: AMD Model Area Estimation                                  | 44 |

| Figure 3.13: Embedded DPCAM Area Estimation                             | 44 |

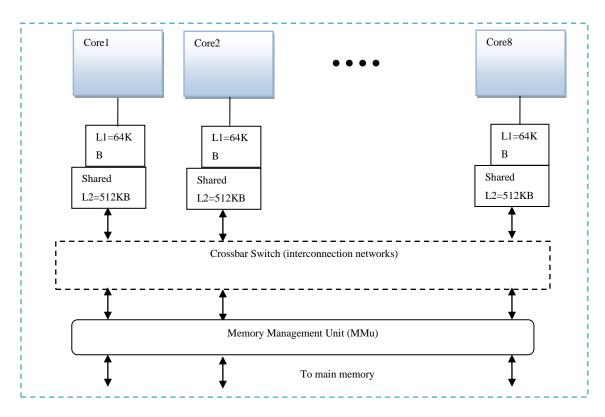

| Figure 4.1: AMD Multi-core Architecture                                 | 47 |

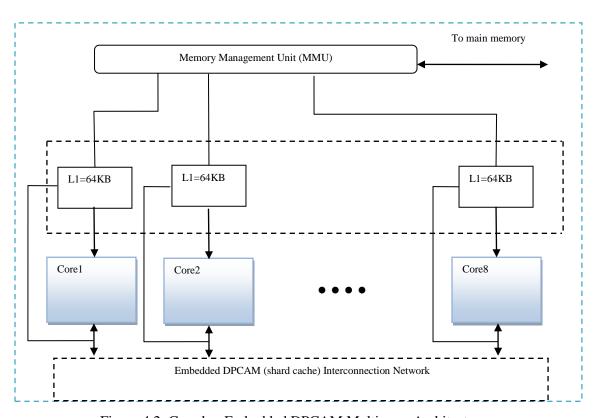

| Figure 4.2: Crossbar Embedded DPCAM Multi-core Architecture             | 48 |

| Figure 4.3: (pp) Benchmarking Program.                                   | 50        |

|--------------------------------------------------------------------------|-----------|

| Figure 4.4: Execution Time in Second (pp) Program.                       | 52        |

| Figure 4.5: Number of Instruction per Core.                              | 53        |

| Figure 4.6: L2 Miss Ratio                                                | 54        |

| Figure 4.7: Invalidation Number per Core                                 | 55        |

| Figure 4.8: (pp) Execution Time in Multi-core                            | 56        |

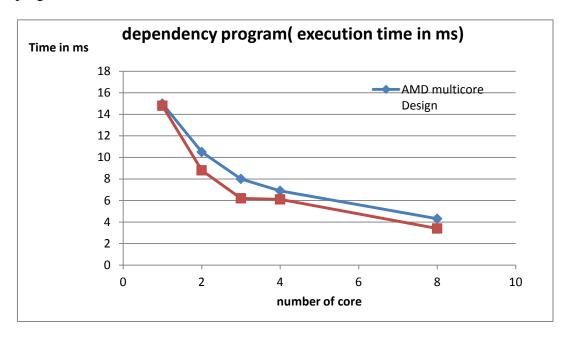

| Figure 4.9: Dependency Program Execution Time in Multi-core              | 57        |

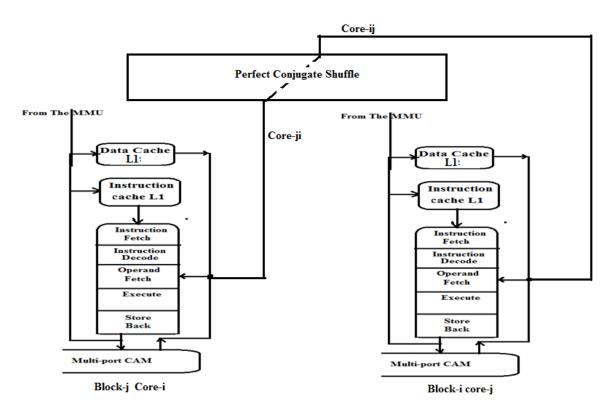

| Figure 5.1: Connecting to Cores in Two Fifferent Block via the Perfect C | Conjugate |

| Shuffle                                                                  | 60        |

# **Chapter 1**

### Introduction

#### 1.1 Motivation

In shared memory multiprocessor systems, there are three crucial issues to be considered; The interconnection networks and the communication bottleneck problem, the scheduling policy which needs load balancing and true dependency, and the cache coherence problem[Joh07][Chi06][jess96]. All these issues apply equally to the on chip shared memory multi-core processors. Multi-core processors are multiple pipelined processors on a chip. Symmetric shared memory multi-core processors exchange information via shared variables. Shared variables reside in shared memory modules and are accessible by all cores. Accessing the shared memory without delay necessities the existence of efficient interconnection network. Any bottleneck in the network causes delay and hence, degrades the performance of the multiprocessor/multi-core system. Provided that dependence rules are observed in the scheduling policy, the processor needs to read/write the right version of the data. This needs synchronization among the processors through hardware and software cache coherence protocols. Synchronization and cache coherence operations add burden on the communication in the interconnection network. The ideal multiprocessor case occur

when the software perfectly observes the dependence rules and load balancing, and when there is no communication overhead due to the bottleneck in the network and cache coherence operations.

In this thesis we present multi-core architecture to solve the communication among cores and between shared memories, this architecture totally eliminates the bottleneck on the interconnection networks and need for arbitration. It also eliminates the need for cache coherence operations. We can say that, if the program is carefully partitioned and scheduled, it nearly can be executed in time equals to 1/n of the execution time on a single processor, i.e., the speed up of the system is ~n, where n is the number of processors (cores).

#### 1.2 Problem Specification and Justification

Scheduling policy is other problems were migrated from discrete multiprocessor to multicore processor. Scheduling policy is concerned with dividing program among the

processors to be executed in shortest possible time. Scheduling problem will be discussed

in next chapter. Scheduling involves partitioning the program into chunks (nodes, grains)

and scheduling these chunks to the processors without violating the dependence rules. The

nodes have local and shared variable. The local variable is accessible by its node only,

whereas the shared variable is accessible by all nodes which need them. Access by number

of node must be synchronized so that the node reads or writes the correct version of data.

Hardware synchronization and software cache coherence protocols are needed.

All multi-core architecture has distributed cache Level, level1 (L1), level2 (L2) and in some cases level3 (L3) caches which must be coordinated. Multi-core architecture uses

shared caches among the cores. This led us to the last and main problem which is the communication among the cores through accessing shared variables.

In the next chapter we will discussed these two problems; the communication via the interconnection network and the scheduling including the cache coherence operations. Then the proposed architecture will be justified in details. A primary justification is the elimination of these problems and their overhead.

#### 1.3 Thesis Contribution

In modern on-chip multi-core processor systems [Intel12, AMD07, Joh07, Tor10], the communication between the processor cores and the shared cache modules of the system suffers from a bottleneck problem that negatively affects the performance of system. So we proposed a multi-pipelined processor on a chip to solve these problems. In this model we have designed a new interconnection networks based of small cache organization modules that are embedded at the cross points of the crossbar network. It provides a non blocking communication among the cores of the system and the shared memory module including snooping cache coherence at the same time. This organization, i.e., the network plus the dual port CAM (DPCAM) modules, has formed a multiport content addressable memory (MPCAM).

#### 1.4 Thesis Organization

The remaining chapter in this thesis are organized as follows. In the chapter 2, we will discuss the modern multi-core system architecture and analyse its main problems; the contention in the interconnection network, the scheduling policy and the cache coherence. In the chapter 3, we will present the above design, its mathematical model and the results

of its performance as standalone component. In chapter 4, we will display the simulation results within the multi-core architecture and compare it with AMD multi-core architecture. In chapter 5, conclusion and future work will be drawn.

### Chapter 2

# **Background and Related Work**

#### 2.1 Current Approach

#### 2.1.1 Multiprocessors Systems

The main idea for using the Multiple Processors (MP) is to increase the performance of system. It presents a great hope for massive parallel processing. The multiprocessor computer system is the use of two or more central processing units (CPUs) within a single computer system.

According to Flynn classification of computers, multiprocessor systems are classified as Multiple Instruction Stream Multiple Data Stream computers (MIMD) [Barry96]. In this class of Computers, a number of processors can execute multiple streams of program instructions which operate on a number of different data streams simultaneously.

Multiprocessor systems are divided into two major classes; tightly coupled and loosely coupled [Joh07]. Loosely coupled multiprocessors are run on multicomputer system and use message passing techniques over the computer networks to communicate among the processes running on different computers. Tightly coupled multiprocessors [M.Ab12] is widely used in multiprocessor computer architecture. Tightly coupled mostly execute single program on a number of processors that share a space of memory of the same computer. Communication among the processes on different processors takes place via

shared variable in the shared memory. These variables are accessible by all the processors of the system.

Multiprocessor power can, theoretically, be expanded to any scale we like. The processing power of a multiprocessor System can be increased; simply by adding more processing elements (PEs) to the system. However, expanding a multiprocessor system is not as straightforward as it looks. There are many issues usually have to be resolved. In this thesis we have proposed design and simulate new shared cache modules and interconnection network organization to improve the communication between PEs (cores) and to eliminate the bottleneck. The network plus the memory modules result in a new component called Multi-Port Content Addressable Memory MPCAM. Used as a second level shared cache in the multi-core processor system.

#### 2.1.2 Multi-core System

With the tremendous advent of semiconductor technology in the last two decades, Integrated circuit (IC) that integrates all components of a computer or other electronic system into a single chip is called system on a chip (SoC). As a result, it became possible to implement a number of pipelined processors (cores) with their caches and interconnection network on one chip named multi-core processor. All pros and cons of multiprocessors have moved with them from on-board to on-chip. They have the same architectural issues problems. The two extra problems is the space allowed on the chip because as Moore's Law said (the doubling of transistors on chip every 18 months) [Moo74] and the power temperature consumption of multiple core on a single chip, which limits the number of implemented processors. These extra problems tended to be solved in recent years.

#### 2.2 Alternate Approach

#### 2.2.1 Multi-core Processor Architecture

As we explained on a chip multiprocessors (OCM), known as multi-core processor. This involves a number of pipelined processor implemented on a single chip. This can be considered as tightly-coupled multiprocessor on a chip. Mainframe systems with multiple processors are often tightly-coupled [M.Ab12].

Multi-core systems architecture is divided into two architecture classes; Symmetric Shared Memory (SSM) systems and Distributed Shared Memory (DSM) systems. These two classes will be discussed later.

In OCM systems, three major issues are of prime concern; they have the same architectural problems as discrete multiprocessor system, namely, the effective scheduling policy and the effective communication among the processor elements PEs of the system. A third issue is the cache coherence among the processors of the system.

#### 2.2.1.1 The SSM Multi-core Processor Architecture

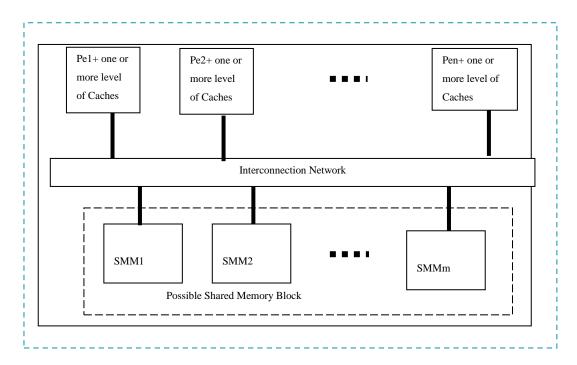

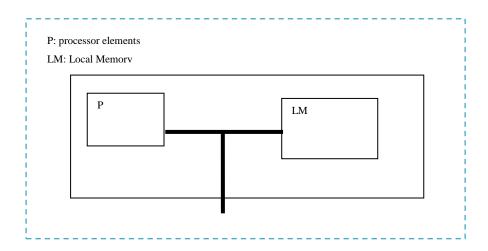

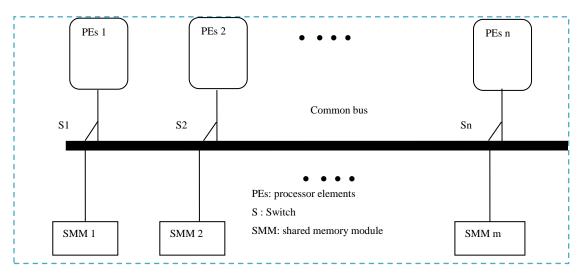

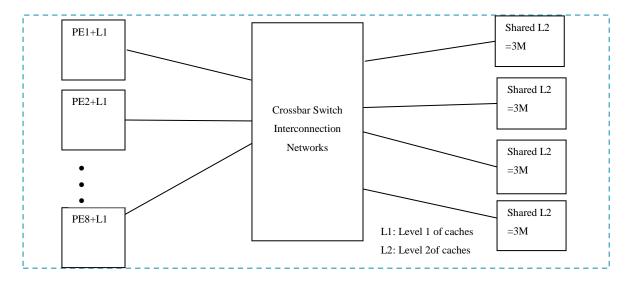

In this type of architecture the cores and the shared memory modules are placed on different sides of the interconnection network. Each core includes a pipelined processor and one or two levels of local cache. Figure (2.1-a) depicts a block diagram of a typical SSM system, and figure (2.1-b) depicts a processing element of the system.

Going through this architecture, we can note the following things:

1- Any processor can access any shared memory module through the supposed interconnection network.

- 2- Even with the best network (crossbar switch) there is still a bottleneck when more than one processor tries to access the same module at the same time.

- 3- The cache coherence policy puts a severe overhead and bottleneck on the network.

Only one processor can broadcast the latest version of the data at a time. All these issues will increase the latency [Joh07].

Figure 2.1(a): A Block Diagram of SMM System [Joh07].

Figure 2.1(b): Processing Elements (PEs) [Barry96].

#### 2.2.1.2 DSM Multi-core Processor Architecture

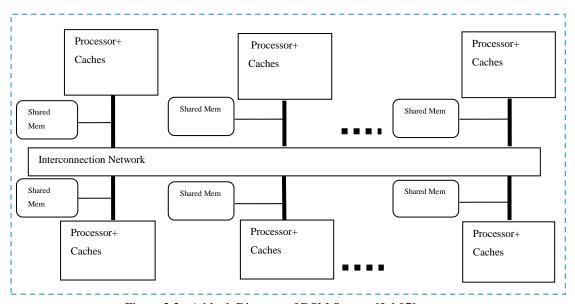

In this architecture, each core has its own part of shared cache in addition to its local caches connected to the core local bus as shown in figure 2.2. A survey of these systems is shown in [Joh07] [Pro96]. All cores are connected to the interconnection network. The computational task must communicate with one or more remote processors. In this architecture, we can note the following:

- 1- Each processor can access any shared memory which belongs to other processor via the interconnection network.

- 2- This architecture also has the same communication bottleneck (even for best interconnection network; the crossbar switch).

- 3- Also the cache coherence presents a heavy overhead on the network.

New DSM architectures are organized called a hybrid Distributed Shared Memory. The main goal of hybrid DSM organization is to support fast physical memory accesses for private data [Xia11].

Figure 2.2: A block Diagram of DSM System [Joh07].

#### 2.2.2 Multithreading and Micro-threading

In Von Neumann model architecture, the instruction is executed when its turn comes on the program counter, whereas in dataflow model, the instruction becomes ready to execute when its operands are available. If dataflow is applied on the instruction level, massive parallelism is expected. Applying dataflow model on the instructional level is referred to as fine grain dataflow, and produces high degree of parallelism [D.E99]. In early eighties, several dataflow multiprocessor systems were built in USA and Europe. However, the results represented disappointment to the builders of these machines. This is because applying parallelism on instructional level necessitates exchanging large number of variables among the system PEs through the interconnection network. This leads to a network congestion, which means a large delay in communicating the variables, hence a large delay in executing the supposed ready-to-execute instructions [Barry96] [Fira01]. The result is a whole degradation of parallelism of the system. Large grain dataflow represented a solution for the congestion problem. In this model, the level of parallelism is increased to the grain level where the grain is part of the program of a function, a process or, a task level. The grain includes a number of instructions that are executed sequentially depending on an internal program counter to the grain. A number of independent grains of the program can be executed in parallel. The grain is sent to the queue when its arguments are available. The grains exchange the shared arguments through the interconnection network. The production of arguments is less frequent than the production of operands in the instruction level parallelism. This represents less pressure and less congestion on the network. The optimisation of the grain size is an issue by itself. One needs to choose the size which suits the machine on which he runs the program. Here, we need to introduce multithreading concept before we continue to the micro-threading.

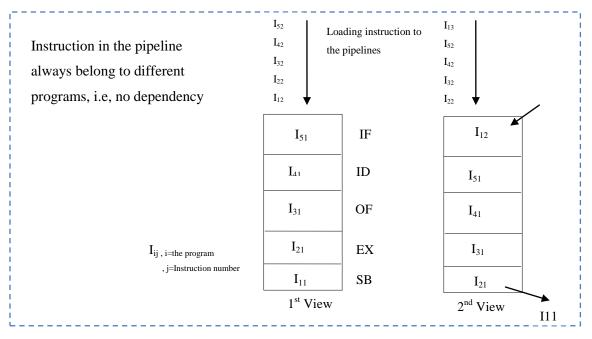

Multithreading was introduced on a single pipelined processor in order to avoid out-of-order and interrupt problems in the pipelined processor. A number of instructions from different programs (threads) equals to the number of the stages of the pipeline are interleaved in the pipeline so that there is no dependency among the instructions [jess01]. This is simply because the instructions belong to different programs (threads). (See figure 2.3).

Figure 2.3: Multithreading Pipelining

The multithreading concept was extended so that threads become independent nodes (grains) of the same program. Again the size of the grain has to be optimal for better parallelism. Through his research, Jesshope and his team found, through statistical analysis, that if the program is divided into grains, each includes a number of instructions nearly equal to the number of the pipeline stages, a maximum parallelism will be obtained. Nodes (grains) of this size were given the name micro-threads [jess01, luo02].

Multithreading use a different set of solutions by utilizing coarse-grained parallelism. A multi threaded processor is able to concurrently execute instructions of different threads of control with a single pipeline [Theo02]. The need for multithreading mechanism in

multiprocessor system, especially in multi-pipelined cores is obvious. In order to use multiple cores simultaneously, multithreading mechanism are required.

Jesshope et. al. [jess96] demonstrated in his work that dynamic scheduling of microthreads on several pipelined processors would result in massive parallelism, reducing the effect of out-of-order instructions in the pipeline.

#### 2.2.3 Valgrind Simulator Tool

We will use simulator called Valgrind which is Open Source / Free Software under GNU/Linux. Valgrind is a runtime instrumentation framework; Valgrind catches all the memory accesses and gives the possibility to analyses these memory accesses. Other tool called Callgrind based to Valgrind which it performs detailed simulation of the L1, L2 and Last Level (LL) caches. Based to Valgrind developed by Josef Weidendorfer [valgrind, Fra08].

Josef Weidendorfer tool of valgrind which is developed at Department of Informatics at the Technical University Munich. This tool is able to handle problems with the cache synchronization, concerning an AMD multi-core system. This tool must handle all the problems occurring on a multi-core system. This tool implements the L1, L2 and LL of caches as the AMD multi-core architecture, crossbar switch interconnection networks where used. The main work in our thesis is to compare the performance of our architecture multi-core system that uses the embedded DPCAM in shared memory with AMD architecture, so we must modify the Valgrind to be simulated with our architecture.

Micro-benchmarking programs were designed to measure the performance of a multi-core system. This will be used to compare the results between AMD and our design. OpenMP is a good micro-benchmarking program to get some concurrent software [Ope08]. This type

of micro-benchmarks program is used to measure the overheads of synchronization, loop scheduling and it has a best feature to be compared in multi-core system.

Several parameters will be tested in this simulator.

- 1. The number of instruction, the program requires running.

- 2. The number of cache hits (hits ratio) in both L1 and L2.

- 3. The number of cache misses (miss ratio) in both L1 and L2.

- 4. The number of invalidation access the shared variable through the networks.

- 5. The execution time delay for the micro-benchmarking program.

#### 2.3 Major Issues in Multi-core System

#### 2.3.1 The Scheduling Policy for Multiprocessor

Regarding to the scheduling policy in multiprocessor systems can be generally defined as how we can execute a set of processes on a set of processors. These criteria called scheduling policy that aimed to minimize the expected runtime (execution time) the program and other parameters as minimizing the cost and the communication delay [Ste02, Rama77].

The Scheduling policy includes two activities; first, partitioning the program into nodes (grains) arranged in a dependence graph, where the node size varies from one instruction to a process or a task [Barry96], and second assigning the nodes to the processing elements of the system. The portioning policy decides the level of parallelism, where as the assignment policy decides whether the scheduling policy is static (deterministic) or dynamic [jess96]. In static scheduling, the nodes are assigned to the processing elements (PEs) (the pipelined cores) at the compile time [Cha10]. The set of nodes assigned to a processing element (without violating the dependency rules) forms a program stream. The program stream is

stored in the local memory of the processing element. PEs executes their streams in parallel. Also, dependency rules across the streams must be observed. Several Static and Dynamic Scheduling in multiprocessor systems were built in the last years, since 1980's this issue has been over killed by research [Fang90, C.D88]. Easily one can find a scheduling policy that suits his architecture. Therefore, this is outside the subject of our research.

#### **2.3.2** Communication among the Cores

Regarding to the communication issue, it implies that the interconnection network must provide effective communication among the processors and between the processors and the shared memory in both SSM and DSM in figure 2.1 and figure 2.2. This issue represents the core of this thesis.

Several topologies of multiprocessor interconnection networks were designed, implemented, and tested. Common shared bus, multiple bus, crossbar switch, multistage interconnection networks (Omega, Butterfly...), and tree and mesh topology are examples [Imr07]. All of them suffer from a bottleneck when more than one processor accesses the shared bus or when they request the same memory module. These different interconnection networks will be discussed in later sections.

Also, two communication strategies among the PEs (the cores) of the system were identified; communication through shared variables, and message passing communication [Barry96]. The shared variable communication needs synchronization in order to make sure that the PEs are accessing the variable in the right time and the right order to satisfy best and correct performance. This issue causes the cache coherence problem which needs the synchronization of the variables among caches in each core.

#### 2.3.3 Cache Coherence Issue

As we explain in the communication issue the bottleneck happen when more than one core need to access the same module at the same time. The cache coherence is the second problem which adds burden to the interconnection networks.

Cache coherence is a concern in all multi-core architecture because in all shared memory multi-core system, each core has its own distributed L1, L2 and L3 caches [Intel12] [Bar08]. Since each core has its own caches, the copy of the data in that cache may not always be the most up-to-date version. It is possible to have many copies, one copy may store in the main memory another copies in each cache memory. Therefore when one copy in any location is changed all other copy must be changed also, Figure 2.4 illustrates the cache coherence problem and shows how two different processors in dual core system can have two different values for the same location. This difficulty is generally referred to as the cache coherence problem. Without any additional precautions we can see different versions of the same variable in each core [Joh07].

| Time | event               | Cache content for core 1 | Cache content for core 2 | Memory content for |

|------|---------------------|--------------------------|--------------------------|--------------------|

|      |                     |                          |                          | Location X         |

| 0    |                     |                          |                          | 1                  |

| 1    | Core 1 read X       | 1                        |                          | 1                  |

| 2    | Core2 read X        | 1                        | 1                        | 1                  |

| 3    | Core 1 store 0 to X | 0                        | 1                        | 0                  |

Figure 2.4: The Cache Coherence Problem in Dual Core System [Joh07]

#### 2.3.3.1 Cache Coherence Protocols

A cache coherency protocol is a protocol that preserves the consistency between all caches in shared memory system [Arch86]. In general in multi-core architecture there are two protocols for cache coherence, a snooping protocol and a directory-based protocol.

The snooping protocol always works with a buses based system, and use number of different states to decide if the value must be updated or not. The simple way is to broadcast the update value to all caches.

The directory-based protocol can be used on any networks; it is scalable to many cores, in contrast to snooping protocol which is not scalable. In this protocol a directory is used that holds information about which memory locations are being shared in multiple caches. Also, it knows when it needs to be invalidated. As in snooping protocol, directory-based protocol use number of states to decide if the value is valid or invalid. Most modern architecture use Modified, Exclusive, shared and Invalid (MESI) states Modified Data means the cache data can be read and written locally without accessing the bus system. Exclusive as modified means that data are in one cache only, but it has not modified at all, and is exactly the same as in main memory. Shared means that the data are held in more than one cache and this cache data are up to date. Invalid means that the cache data defined as invalid if the cache line is empty, or data in it are invalid [Joh07]. In the last years different protocol have been proposed with different number of states as (MSI) and (ESI) [AMD07].

In all interconnection networks the cache coherence protocol puts a severe overhead and bottleneck on the network. Only one processor can broadcast the latest version of the data at a time. Also adding more cores in multi-core system has more impact on the amount of time necessary to validate the protocol [M.Zah10]. So, it poses a scalability problem.

In this work, we present a multi-core system architecture in which the communication medium solves and nearly eliminates the problems of bottleneck, the latency, the cache coherence and the scalability of the system. In the following sections, the traditional networks will be introduced in order to pave the way for clearing the features of the proposed architecture in chapter 3.

#### 2.4 Interconnection Networks in Multi-core Architecture

In this section we will discuss the common Networks on a Chip (NoC) used in multi-core system, the discussion will include the networks topologies with some of its problems and the performance of these networks.

#### 2.4.1 The Common Bus Networks

The common bus is the first and simplest interconnection topology. It is a shared path to which all units of the system are connected figure 2.5.

Figure 2.5: Common Bus Interconnection Networks [Edw86].

The common bus is the least complex and easiest to configure. The common bus represents a bottleneck by itself. It can serve only one communication request at a time, so to prevent

contention on the bus an arbitrator is used and any core need to use the networks must first request the arbitrator to determine the bus status [Edw86].

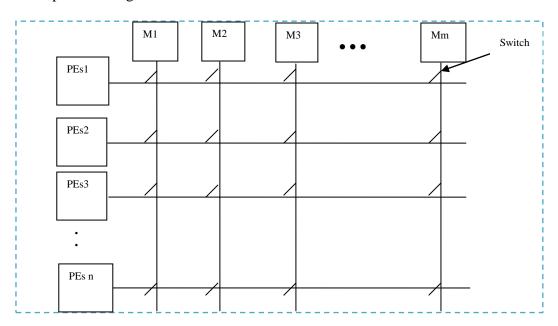

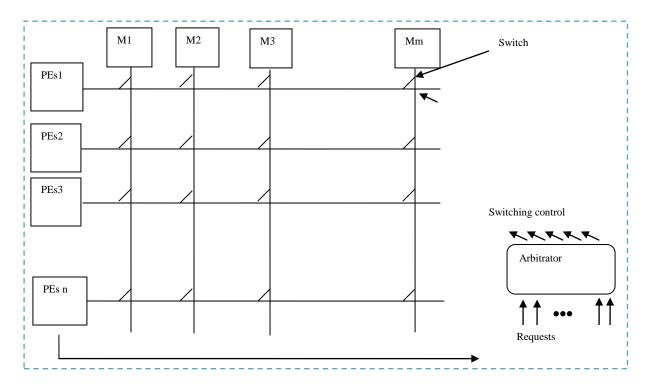

#### 2.4.2 The Crossbar Switch Networks

Crossbar switch networks are obtained by increasing the number of buses for every core and memory module in horizontal and vertical links, such that buses can be accessed at cross points as Figure 2.6.

Figure 2.6: Crossbar Switch Interconnection Networks [Imr07].

The number of vertical and horizontal buses equal the number of PEs and memory module. The crossbar switch is the most effective interconnection network. It has complete connectivity with memory module. However, the conflict appears if more than one source request is competing for the same memory module. This case is called memory interference. Only one request will be served [Imr07]. To solve this conflict, every bus leading to a memory module must be provided with an arbitrator see Figure 2.7. But the arbitrator adds to the implementation of crossbar more complexity and cost when we increase the number of processors.

Figure 2.7: Crossbar Switch with Arbitrator Interconnection Networks [Imr07].

Crossbar networks can be improved by including small buffers at sources and destinations this called buffered crossbar. In last year many research were published and suggested in this topic, Critical internal Buffer First (CBF), input queued (IQ) and internally buffered crossbar (IBC) switches [Lot05].

More recent papers focused on the development of the arbitrator in different networks. Some paper suggested a new design by adding an asynchronous First IN First Out (FIFO) after each processor requests to hide the delay of waiting time during request. But it still requires a complex arbitrator [Moor02, Rig02]. Other mechanism create intelligent arbitrator that provides priority for processor to make request, it is shown that this arbitrator can be extended easily to support large numbers of processors [Has06].

To conclude we can say that the crossbar switch is the most effective interconnection network [Lan82] and the most modern multi-core system adopts this interconnection networks, but it still suffer from bottleneck. In addition to the problem of the cost and

complexity of crossbar grows rapidly as a function of square of inputs number, where if N is the number of processors then the number of switches equal N<sup>2</sup>.

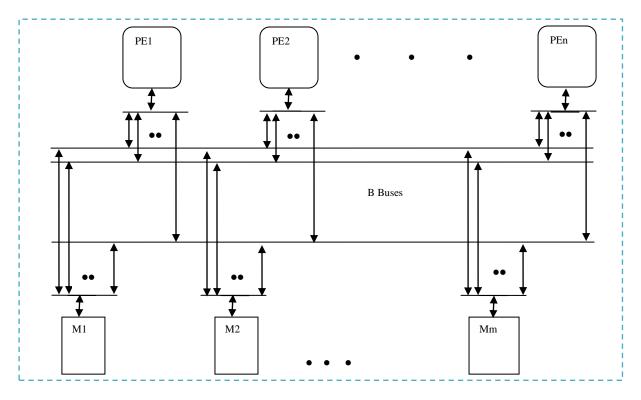

#### 2.4.3 The Multiple Bus Network

Crossbar network is meant to include same number of cores and memory modules. This to meet the demand of the processor at a rate of a request per processor in each cycle. But after each request the processors do an internal operation after each request so the probability to make new request will drop from 1 to 0.5 [Ayy93]. Studies have suggested that connecting N processor to M memory using number of shared buses B equal to half the number of processors, pluses one, this design called multiple bus networks as we explain in Figure 2.8.

Figure 2.8: Multiple Bus Interconnection Networks [Ayy93].

The Multiple bus can serve only a number of requests less than or equal to the number of buses. If two or more requests are going to the same shared memory module, only one of them can be served [Mud84].

#### 2.4.4 Multistage Interconnection Networks

Multistage Interconnection Networks (MINs) are mostly used in parallel multiprocessors systems to connect processors to processors and/or to memory modules [Imr07]. Crossbar switch provides a full connection between source and destination. But, as we mentioned the cost and complexity of crossbar grows rapidly as a function of square of inputs number (in a full crossbar the number of inputs, N, equal the number of outputs). If the 2 x 2 switching elements are used in building a crossbar system then the number of switching elements needed is  $(N/2)^2$ .

In MINs we can use different size of switching elements 2 x 2, 4 x 2 or any size, the most commonly used size of the switching elements is the 2 x 2 switching elements. Hwang and Briggs [Hwa93] have shown how to provide complete interconnection of one set of N devices to another set of N devices using multistage network of  $\log_2 N$  stages with N/2 switching elements of size 2 x 2 in each stage.

There exists various types of MINs where proposed and implemented as Delta networks, Omega networks, Butterfly networks, Self Routing and shuffle-exchange MINs [Barry96] [Chi06, Bhu89, Var89]. The difference between each of these networks is the topology of interconnection links between the crossbar stages. In all MINs if more than one request need the same intermediate link or the same destination shared module, bottleneck will be happened then only one of them will be served as we shown in Figure 2.9.

Figure 2.9: Multistage Interconnections (MIN) with 2 x2 Switch Elements [Imr07]

#### 2.5 Network on Chip on Modern Multi-core System

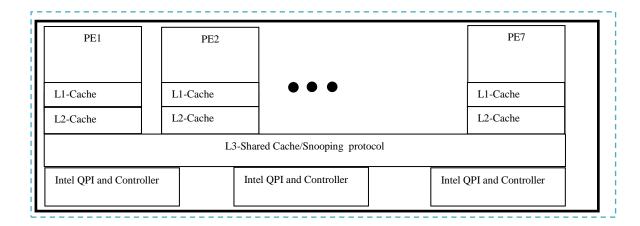

The most modern multi-core system use different Network on Chip (NoC) to communicate between processors and shared memories. Sun T1 is a multi-core multiprocessor introduced by Sun in 2005 as a server processor; each core has private Level 1 caches, each core access shared level 2 caches via a crossbar switch networks as shown in Figure 2.10 [Joh07]. IN AMD multi-core system use System Request Interface & Crossbar Switch to organize communications among the cores [Bar08]. Intel multi-core especially in Intel i7 add the L3 smart and shared cache and increase its size about 16M to reduce the traffic among the cores. But it still needs buses interface. Intel developed their Quick Path Interconnect bus (QPI), which is a 20 bit wide bus running about 4.8 and 6.4 GHz ,as shown in figure 2.11[Neh11]. All of this topology still suffers of bottleneck problems, and the variable synchronization between caches.

Figure 2.10: The T1 Sun Multi-core Architecture [Joh07].

Figure 2.11: Intel I7 Multi-core Architecture [Neh11].

#### 2.6 Types of Cache Memory

There are three types of cache organization; the direct mapping, the set associative and the fully associative cache.

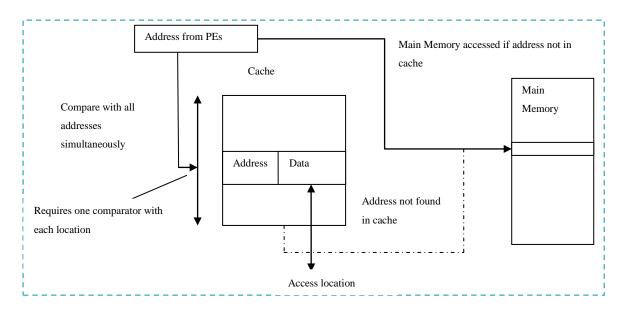

#### 2.6.1 Fully Associative

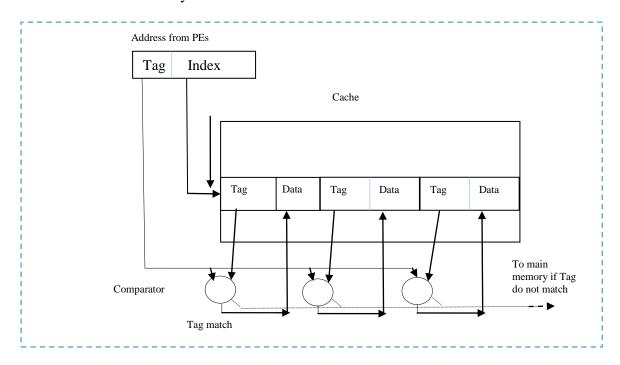

In this type of cache both memory address and data are store in the cache. The memory is of the Content Addressable Memory (CAM) type. Memory address is simultaneously compared with all addresses store in caches using the internal comparator in each location. Figure 2.12 illustrates the architecture of fully associative cache memory.

The main advantage of fully associative cache is its high performance compared to its size. The main disadvantage of the CAM cache is the complexity in design and the cost. Also, the fully associative cache needs an algorithm to select where to store information in it. Different algorithms were used to solve this problem, as Random Selection, First In First Out (FIFO) and Least Recently Used algorithm (LRU) [Sha96] [Bary96]. The Content-addressable memory (CAM) is a special type of fully associative cache.

Figure 2.12: Fully Associative Cache Memory [Barry96]

#### 2.6.2 Direct Mapped

In this case, the memory is divided into blocks called sets. So in one cache line we can hold one entry of a set of the main memory. The main advantages of this type are very easy and cheap to implement, but the performance will be dropped if accesses are made to different locations with the same index.

#### 2.6.3 Set-Associative Mapping

This is a combination between a fully associative cache and a direct mapped cache. Cache divided into sets of lines. One address of a set of the main memory can be stored in n possible cache. It is not as complex as fully associative cache, but offers an improvement of performance because more than one address can be stored. Figure 2.13 represent set associative cache memory.

Figure 2.13: Set Associative Cache Memory [Barry96]

#### 2.7 Cache Events Classification

When a processor accesses the data, the data may be cached or not. These two events are called cache-hit and cache-miss. A cache-hit and cache-miss may occur on any level of caches. Both cache hit and miss are an important event when looking to cache coherency. In this section we will focus on how miss and hit cache exactly works?

#### 2.7.1 Cache-Hit and Cache-Miss

Usually, the processor presents its request for data to both cache and the main memory. If the data found in the cache, the processor cache it within its cycle time and the main memory is informed. This is called a cache hit case. If the data not found in the cache, the processor has to wait for the slow response of the main memory. Upon receiving the data, a copy of it is kept in the cache for future accesses. This is called a cache miss case.

Cache-Miss can be classified into four types [Rob08] [Joh07].

- 1- Cold Miss: the processor requests the data for the first time and data is not stored in the cache system.

- 2- Capacity Miss: because the cache size is limited, some data was stored in the cache, but it has been replaced with new data.

- 3- Conflict Miss: we can't store some data in a set associative cache because the number of blocks is limited. Thus a miss occurs, but this type can be avoided in fully associative cache.

- 4- Coherency Miss: this kind of misses happened when processor writes some data. The cache line in other cache has to be invalidated so when other processor accesses these data a coherency miss occurs (these data called shared variable). This type of miss is the most important miss associated with multi-core systems, more techniques proposed to reduce this type of miss[Hyu09][Jae04][ Mil12][Che10]. So in our multi-core architecture design simulator Coherency Miss is the biggest concern to reduce miss ratio as we will explain in chapter 4.

#### 2.8 Embedded Memory Unit Crossbars Interconnection Networks

In 1995, Ayyad and Radolf designed, implemented and successfully tested an embedded crossbar buffer using 4 Kbyte (2KbytesX2) FIFO memories [Ayy96]. The design was implemented on board to connect four of the 32 Intel 486 motherboards of The Makbilan Multiprocessor at Hebrew University. Makbilan was a DSM system. At that time the FPGA technology was not advanced enough to accommodate this architecture. Message passing and packets were used to send, multicast, or broadcast messages from source/s to destination/s simultaneously.16-bit data buses were used. Packetizing, de-packetizing, and storing the received data in the right local destination memory location/s represented a considerable communication overhead.

New designs of Dual Port content addressable memory (DPCAM) was suggested; a port for reading and another for writing. Under the supervision of Abu-Mwais, two students (S. Surkhy and A. shawar) managed to implements the idea using Veriloge language. Later, the author modified this design, then successfully implemented and simulated it. In the next chapter, the architecture of this memory will be presented.

After that we took this as a basis for multiport CAM (MPCAM). CAM is not feasible to be implemented as a standalone memory (we need very large number of pins). However it proved too useful as a part of multi-core architecture if implemented as shared memory. Also, it proved useful for fast cache coherence. So we decided to design and simulate it as a part of multi-core architecture as we will show in chapter 4.

## Chapter 3

# The Design of New Crossbar

### **Embedded DPCAM and the**

### **Simulation Results**

### 3.1 Cache Memory in Multi-core System

There has been always a speed gap between processor and memory [Car02, Pat97]. A great deal of the researchers' effort went to narrow this gap. Cache memory is extremely fast memory that is built into processor to decrease the speed gap between the processor and the main memory. In fact, cache memory responds to the processor request in the real time, and the processor does not need to insert wait states. The processor uses cache to store instructions and data that are repeatedly needed to run programs, when processor access data, it normally fetches it from main memory, this access need long time as compared with the cache. If data already stored in the cache, the processor does not need to wait. The cache responds within the processor cycle. This improves the overall system performance. There are different types of cache as we will discuss later in this chapter.

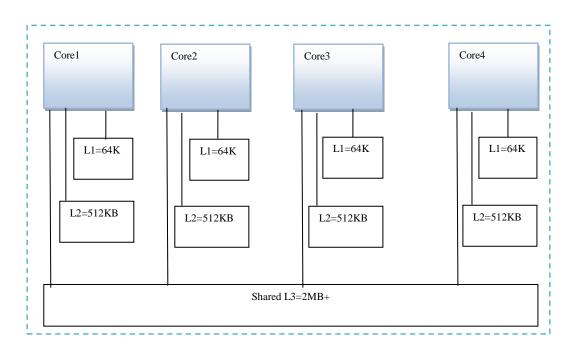

The most modern multi-core systems use more than on level of cache [Intel12][Neh11]. As figure 3.1 illustrates, the AMD Barcelona multicore system [AMD07], Level 1 (L1) of the cache is the fastest one and is directly next to the PEs (the cores) with 64KB per core. L1-Cache in AMD multi-core architecture exists in two versions. One for data, and the other for instructions. They are Called L1D for data and L1I for instructions. The second cache is Cache level 2 (L2-cache) with 512 KB per core followed by the third level of cache (L3). Cache L3 represents the shared memory with total size about 3MB. This multilevel of caches required to improve the communications between cores in multi-core system, thus synchronization between all these caches is required.

Figure 3.1: AMD Multi-core Cache Level [AMD07]

### 3.2 The Design of Dual-Port CAM and Multi-Port CAM

The widespread application of multi-core system makes cache memory highly accessible by the cores of the system. The multi-port cache memory can provide the needed accessibility to multiple cores. In this section, we propose a Dual Port CAM (DPCAM) to be used as an integrated part of a new crossbar interconnection network organization. This organization results in what we call Multi-Port CAM. This MPCAM guarantees that all cores of the system can access data for read and write operations simultaneously. Queuing, contention and the need for arbitration are totally eliminated. Also, as large number of data versions can be accommodated in this MPCAM and accessed by presenting their unique tags, the cache coherence problem is totally eliminated because each core broadcast the last version of shared variable to other cores, so the variables always update.

#### 3.2.1 Single Port CAM

Content Addressable Memory CAM is a memory which its locations are accessed through comparing Tags rather than providing their addresses. In 1980s, the designers of dataflow machines badly needed these devices. However, the available semiconductor technology did not allow implementing large CAMs at that time. Small CAMs (up to 64 memory location CAMs) were available). So, designers resorted to employ RAMs as lookup tables in order to emulate the CAMs. With the advent in semiconductor technology, large CAMs are available now (an order of 100 Kbytes CAMs). Also, universal dual port cache memories have been designed [Kos06, Ara12, Hassa05].

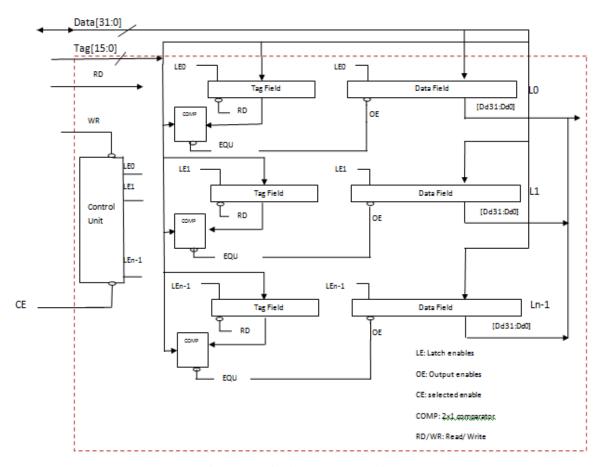

In CAM, each stored data is associated with a unique tag. When we like to retrieve the data, we apply its tag with a read signal to all locations simultaneously. The applied tag is compared with all stored tags simultaneously. If any of the stored tags matches the applied tag, the equality signal of the location comparator enables the output of the location, and the data is placed on the data bus in order to be read by the processor. Figure 3.2 depicts a single port CAM.

Figure 3.2: Single Port CAM Design

#### 3.2.2 Dual Port CAM

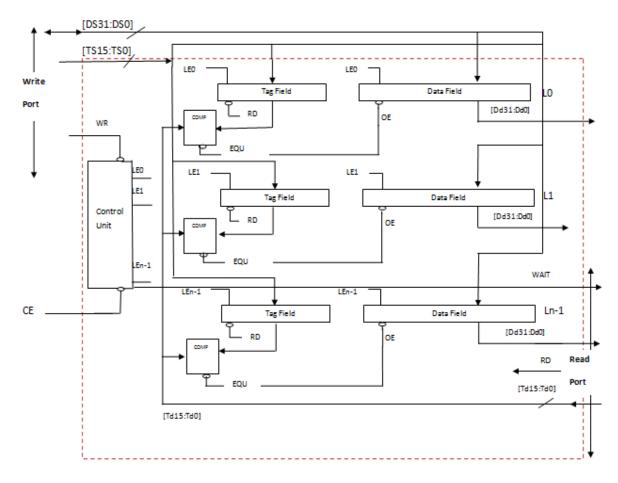

In our crossbar embedded CAM interconnection network among multi-core the need arises for implementing a Dual Port CAM (DPCAM) cache memory modules at the cross-points of the crossbar; to overcome the problems in memory as addressing and unused spaces. The shared data will be residing in these modules and simultaneously accessed by all cores.

These DPCAMs have two ports; one for writing (broadcasting), and the other for reading. They allow simultaneous access operations from the two ports as far as they are not accessing the same memory location. In our organization we only need one port to write, and the other to read, including writing and reading to the same location. This is because in our crossbar embedded cache organization, simultaneous writing and reading on the same

location is likely to happen even with very small probability. The fact that we are designing this DPCAM to meet the needs of our cache organization has affected our design decisions. This included the data width, the tag size, the storage type, and the control circuit of the cache module.

With reference to figure 3.3, in this design, each memory line is composed of two fields; the data field and the tag field. The length of each field depends on the architecture in which the CAM is used. The data field can be 32 or 64 bits in order to go with 32 or 64 bit processors. The tag field can be varied to suit the number of shared data versions, e.g., 32 bit tag can accommodate up to 4 Giga versions of data.

Figure 3.3: The Dual Port CAM Design

The writing process is controlled by the control circuit and the WR signal. The control circuit of the DPCAM includes a pointer to produce an active high Latch Enable (LE)

signal for each memory line on a rotating basis. When the system is reset, this pointer points to the LEO first memory location, so that the first writing operation will be performed on line 0 of the memory. After writing to the current location, the pointer points to the next location, and so on until Ln-1. In the case of simultaneous write and read process, the circuit gives the priority for writing and gives the reading processor a WAIT signal. The WAIT signal can be obtained by ORing the active low RD and WR signal coming from the writing and the reading processors.

The Store Back (SB) of writing core provides the data [Ds31-Ds0], the tag [Ts15-Ts0] (the tag can be the address plus the version number), and the active low WR signal. With the rising edge of WR signal (the end of WR), the control circuit moves the LE to LE1 in preparation for the next writing which will be to line 1. This process can be repeated until LEn-1 is reached, after which it moves back to LE0 where it starts the overwriting process over the old data and tags. The memory lines are made of latches which means that the writing process is level triggered.

The READ process occurs when the Operand Fetch stage (OF) of the reading core applies the destination tag [Td15-Td0], and an active low read (RD) signal to all tag fields simultaneously. The RD signal outputs the stored source tags to the comparator of each memory line in order to be compared with the applied tag simultaneously. If a match occurs, the equality signal (EQU) of the comparator is used as an output enable (OE) signal which outputs the stored data from the data field to the destination data bus where it can be read by the OF unit of the reading core.

#### 3.2.3 Multi Port CAM

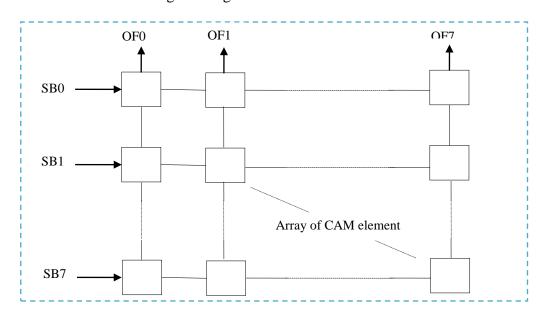

In the proposed architecture in figure 3.4 we have redesigned the shared cache to become a two dimensional array of DPCAM elements. The number of rows and columns of the array are equal and equals the number of the pipelined cores. An extra row is added for the primary shared data which will be loaded by the global memory management unit. This design eliminates the need for arbitration because there is no contention. Also, this cache eliminates the need for global register.

Figure 3.4: The Multi-port Content Addressable Memory

#### 3.3 The Crossbar Embedded DPCAM Architecture (The MPCAM)

In chapter two we discussed the problems in different type of interconnection networks in DSM and SSM multiprocessor. All problems come from the fact that, in spite of moving the architecture into the chip, the designers are still stuck with the past usage of the offshelf components and using in the same way they were used on the printed circuit board (PCB). There is no reason to suggest that the cache must be one piece and no busses can be implemented within the cache architecture. In Fact Crossbar like buses can be embedded

among a matrix of small caches. This is the same as saying "Small cache modules can be embedded at the cross points of a crossbar architecture". So the DPCAM which we designed and simulated can be implemented at the cross points of the crossbar.

In our design in figure 3.4, a SSM Multi-core architecture is assumed, where the shared cache modules are distributed on the cross points of the crossbar. The Store Back (SB) of the pipelined core is connected to the horizontal buses, and the Operand Fetch (OF) units of these cores are connected to the vertical buses of the network. The shared cache modules are specially designed (DPCAM) modules. While loading a program stream, the memory management unit, which loads the instructions and the data to cache L1, loads the primary shared data to the last row of DPCAMs in the MPCAM. This organization is considered cache L2 in our proposed architecture.

#### 3.3.1 The Claims for Embedded DPCAM Networks

With the above MPCAM organization we can claim the following:

- 1. SBs of all cores can broadcast data, each to the DPCAM modules in its row simultaneously. There is no queuing and no arbitration. Note that this is not the case if the modules were placed on the edge of the crossbar as in the usual way, where the broadcast forces queuing with severe latency.

- 2. OFs of all cores can search for the data, each in the CAM modules of its column simultaneously. Also, there is no queuing and hence, no arbitration is needed.

- In the writing (broadcasting) process, the DPCAM module is designed to place the data in the first empty (or least recently written to) location. So, there is no unused memory location.

- 4. The data in the DPCAM location won't be overwritten before n clock cycles elapses, where n is the number of memory lines in the module. The compiler and the scheduler must guarantee the usage of data within the allowed time. Also, if the core needs the read version of data for beyond the allowed time, it can keep it in its local cache.

- 5. As an alternative to point 4, we can implement two DPCAM modules at each cross point; one for short reaching and the other (less frequently used) for far reaching communication. The cores will be less frequently writing to the far reaching parts so that longer time elapsed before they need to overwrite a datum.

#### 3.3.2 The Mathematical Model of Crossbar Embedded DPCAM Network

In this section we will compare the performance of our network design (Crossbar Embedded DPCAM) with normal crossbar switch networks. The bandwidth (BW) is the most important parameter in any multicore system networks (number of requests served by the network). The mathematical models of these networks are derived from probabilities theories. The derivation of the model is based on the model assumptions. For the traditional crossbar and the MPCAM performance models, the following assumptions are made:

- 1- The number of processor cores = (n).

- 2- The probability that a core is making a request to the crossbar network during a cycle is (r).

- 3- In the crossbar switch architecture, **n** processor cores are connected to the row buses of the crossbar. The cross point switch connects the row bus to the required

column bus to which the requested memory module is connected. Not more than a single core can access the destination module at a time.

- 4- In Crossbar embedded cache (MPCAM), n (SB) units of n cores are connected to n row buses, while n (OF) units of the same n cores are connected to the column buses of the crossbar.

- 5- So, 2n units are expected to present requests to the MPCAM, **and 2nr requests** are expected during the cycle.

- 6- As claimed before, all SBs can broadcast and all OFs can read simultaneously, unless two are addressing the same memory location, which has nearly zero probability.

- 7- The **bandwidth** is the number of requests served by the network (**BW**).

- 8- The bandwidth of the crossbar switch is given by equation 3.1 [K.W99, Barry96].

$$BW1 = m - m \left(1 - \frac{r}{m}\right)^n \qquad ... \qquad .3.1$$

Where m is a memory module and n is the processor elements in ideal cases n=m.

9- The bandwidth of crossbar embedded DPCAM is given by equation 3.2.

i.e., provided that the dependency rules are satisfied, all requests will be served.

# 3.3.3 Comparing Results Between Crossbar Embedded DPCAM and Normal Crossbar Switch.

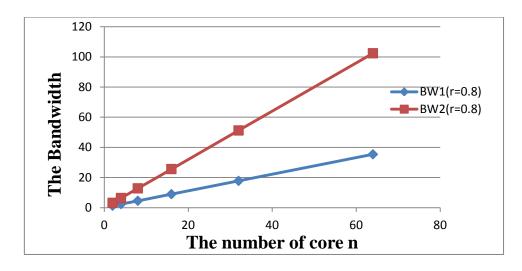

Using the mathematical model in section 3.3.2 we can draw the bandwidth function with different values of r and n, and then we will compare the results from the crossbar embedded DPCAM and the normal crossbar switch. Figure 3.5 to 3.7 show the bandwidth

versus number of cores (n), results shown that bandwidth function increases when the number of core increases linearly.

In figure 3.5 we notice that when r=0.8, in normal crossbar switch the bandwidth always less than number of cores. But in crossbar embedded DPCAM network can serve more requests. In figure 3.5, when (n=64), the bandwidth in crossbar switch about 35 whereas in crossbar embedded DPCAM the bandwidth about 102, when (n=8) the bandwidth in crossbar switch about 5, in crossbar embedded DPCAM the bandwidth about 13. So the crossbar embedded DPCAM can serve more request than normal crossbar.

Figure 3.5: Bandwidth Function with(r=0.8)

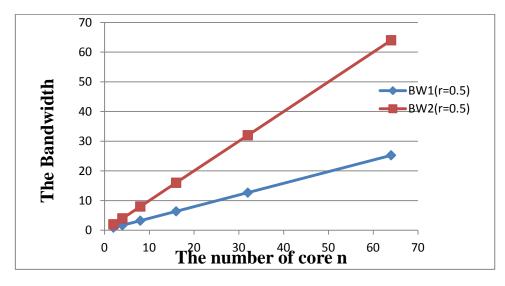

Figure 3.6: Bandwidth Function with(r=0.5)

Figure 3.6 displays the bandwidth function when the r=0.5. This means that the probability to make request from any core is down to half, this cause the reduction of the bandwidth when compared to request rate 0.8. The Crossbar embedded DPCAM still better than normal crossbar switch because there is no competing between cores across the network. When (n=64) the bandwidth in crossbar switch about 25, in crossbar embedded DPCAM the bandwidth about 64. This is due to the fact that in the case of crossbar embedded DPCAM the number of requests is double those of the traditional crossbar. Moreover, the crossbar embedded DPCAM is not blocking, i.e., all the requests are accepted, whereas some are rejected in the case of the traditional crossbar.

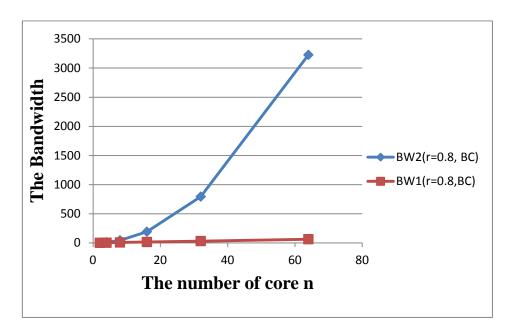

Figure 3.7: Bandwidth Function at Broadcast Situation

Figure 3.7 Depicts the broadcast situation, in normal crossbar switch only one processor can broadcast the shared variable at a time so the maximum bandwidth equals (r(n-1)), while in crossbar embedded DPCAM there is no competition among the cores of the system. So all cores can broadcast their variables and the maximum bandwidth equal (r(n)(n-1)).

In conclusion we can say that the crossbar embedded DPCAM network has better bandwidth than normal crossbar switch. This is because there is no competition between cores in both write and read operation. But in the traditional crossbar switch interconnection networks only read or write (one core) can be served at a time, whereas in our shared cache two cores, one for read and another for write can be served simultaneously.

#### 3.4 Simulation Results of Crossbar Embedded DPCAM Circuit

Using Verilog Hardware Description Language (VHDL) in Quartus II software from ALTERA, DPCAM and the crossbar embedded DPCAM network have been designed and implemented. In our work we use a Stratix III FPGA which has good specifications for this type of design as a target. It provides high-performance, lowest possible power consumption and high-integration capabilities. The main advantage of a Stratix III FPGA actually increase with design size because it has large number of I/O pins and gates compared to other available chips family [Alt08, Alt13]. More of other characteristics can be found in ALTERA-site [Altera]. The simulation results show that latency of less than or equal four nanoseconds per shared variable access in multi-core system has been achieved where the latency to access the shared memory is, approximately, 65 nanoseconds in modern multi-core system [Neh11], and about 40 nanoseconds in Intel multi-core system that use QPI. Figures 3.8 to 3.11 explain the simulation results in both functional and timing simulations.

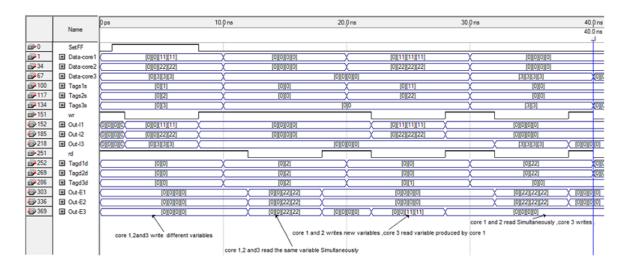

Figure 3.8 shows the functional simulation of crossbar Embedded DPCAM, as we explained in section 3.2.2 for write process core add Data and tags(Tag source) with active low WR signal and in case of read core generate tagd (Tag destination) with active low RD

signal. In functional simulation the outputs appear on the pins without considering the delay of the gates in design. In this figure we have executed the network in different situations. In the first situation all cores write their shared variable simultaneously. In the second situation all cores read the same variable produced by the second core simultaneously. In the third situation both the first and second core write shared variable also the third core read variable produced by first core. Finally both first and second core read simultaneously and the third core writes variable. In all situations we made sure that the embedded DPCAM network operates in multi-core system with full non-blocking and without bottleneck also no arbitration is needed.

Figure 3.8: Crossbar Embedded DPCAM Functional Simulation

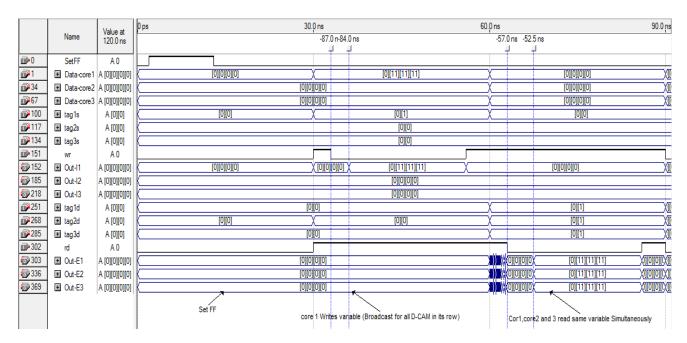

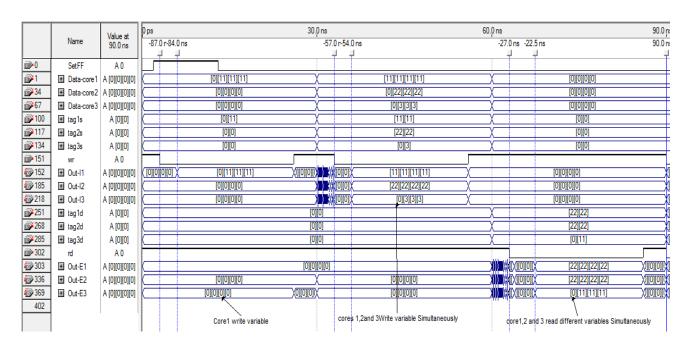

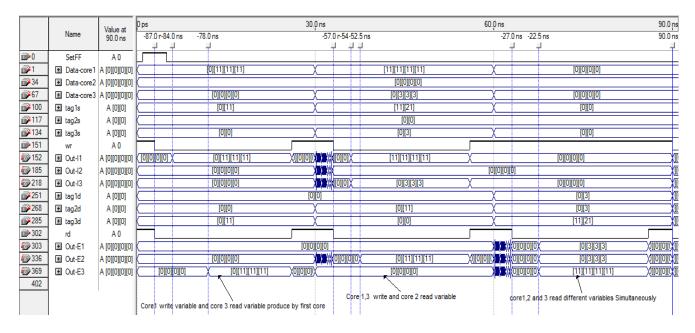

Figures 3.9 to 3.11 show the Timing simulation of crossbar Embedded DPCAM. In timing simulation we can measure the delay of accessing a shared variable in nanosecond. Figure 3.9 shows that when the first core broadcasts variable, the delay is about three nanosecond and when all cores read shared variable simultaneously four and half nanosecond this due to the delay of comparator units. Figure 3.10 shows that when all cores write different variable simultaneously, the delay is about three nanosecond and when all cores read shared variable simultaneously four and half nanosecond. Figure 3.11 displays that when

the first core write shared variable and the third core wants to read the same variable the delay is about three nanosecond for first core and about nine nanosecond for third core. This because when the writing operation has just completed the reading operation starts to compare the tags.

Figure 3.9: Crossbar Embedded DPCAM Timing 1 Simulation

Figure 3.10: Crossbar Embedded DPCAM Timing 2 Simulation

Figure 3.11: Crossbar Embedded DPCAM Timing 3 Simulation

So, this simulation process proved that all cores can access the shared variables in the shared CAM simultaneously without the problems of contention, queuing, and arbitration.

#### 3.5 Area Estimations and Model Complexity

Because the technology continue to shrink and the size of chip continue to be larger. So estimating the area of our proposed architecture would help use in judging this design. In this section we have adopted on published papers, especially for cache estimated area to decide and compare the die area of our model with AMD model. Figure 3.12 displays the total area for AMD multi-core architecture this architecture use two level of caches, L1 as private cache and L2 as shared cache. Figure 3.13 displays the total area for our multi-core architecture this architecture uses two level of caches also, L1 as private cache and L2 (embedded DPCAM) as shared cache.

| Components         | Size of   | $\lambda^2$ Area | Area    | num | Total           | Ref#           |

|--------------------|-----------|------------------|---------|-----|-----------------|----------------|

|                    | cache     |                  | $mm^2$  |     | area            |                |

|                    |           |                  |         |     | mm <sup>2</sup> |                |

| L1 Cache           | 64 KB     | 8.06e+8          | 12.593  | 8   | 100.75          | [Kie98][Lin99] |

|                    | (32I+32D) |                  |         |     |                 |                |

| L2 Cache           | 512 KB    | 7.25e+9          | 113.281 | 8   | 906.24          | [Bat98][Gua09] |

|                    | shard     |                  |         |     |                 |                |

| Total Area         |           |                  |         | l   | 1006.9          |                |

| (mm <sup>2</sup> ) |           |                  |         |     |                 |                |

|                    |           |                  |         |     |                 |                |

Figure 3.12: AMD Model Area Estimation

| Components         | Size      | $\lambda^2$ Area | Area   | num | Total  | Ref#           |

|--------------------|-----------|------------------|--------|-----|--------|----------------|

|                    |           |                  | $mm^2$ |     | area   |                |

|                    |           |                  |        |     | $mm^2$ |                |

| L1 Cache           | 64 KB     | 8.06e+8          | 12.593 | 8   | 100.75 | [Kie98][Lin99] |

|                    | (32I+32D) |                  |        |     |        |                |

|                    |           |                  |        |     |        |                |

| Embedded           | 16 KB     | 5.10e+8          | 7.987  | 64  | 511.16 | [Sha02]        |

| DPCAM              | shard     |                  |        |     |        |                |

|                    |           |                  |        |     |        |                |

| Total Area         |           |                  |        |     | 611.91 |                |

| model              |           |                  |        |     |        |                |

| (mm <sup>2</sup> ) |           |                  |        |     |        |                |

Figure 3.13: Embedded DPCAM Model Area Estimation

As stated earlier, the design of the multi-port CAM is meant to allow simultaneous access of a number of cores to the memory. This includes simultaneous writing and reading of the shared variables to and from the memory. As a crossbar topology is used in this design, the cost and complexity is expected to grow as a square function of the number of ports. Note that the number of input ports is equal to the number of output ports. The growth of complexity is limited by two factors; the available silicone area on the chip and the number of pins.

The design of the multiport CAM as a standalone chip is really limited by the number of pins rather than the silicone area. It needs a number of pins equal to 2nw, where n is the number of port and w is the number of pins per port. For example, designing a four 8-byte ports CAM needs 2X4X64= 512 pins. This is we could not design and simulate more than 3-port standalone CAM as targeted to Altera StratixIII FPGA chip which has less than 512 pins[Alt08, Alt13]. However, if the design is integrated as part of a multi-core processor, it is fairly feasible to design eight or sixteen port CAM of 2Mbytes as a shared cache of the processor. This is less than or equal to the shared cache used in Intel and AMD multi-core processors so far.

Regarding the scalability of the system as we will explain in chapter 5, it has been shown in this thesis that if n-core processor with n-port CAM shared cache is feasible, then as far as the available silicone allows, the system can be linearly expanded to n blocks where each block is an n-core processor. This means a system of n square cores. Its cost will be nXc, where c is the cost of the n-core processor. The expected latency is fixed at an average of 1.5t, where t is latency of accessing the local cache or the shred cache (the same) in an n-core processor.

We conclude that the design presented and simulated in this thesis represents a quite simple, efficient, fast, and powerful system.

## Chapter 4

# Simulation Results within Multi-Core System

#### 4.1 AMD Vs. Our Model Architecture

In the AMD multi-core simulator it is necessary to understand the main parts are required for the simulator. The simulator is based on the crossbar switch interconnection network, ESI (Exclusion-Shared-Invalid) cache coherence protocol, and accessing through cache and main memory. In the memory access works as first check whether there is a L1 cache hit, then if there is a L2 cache hit. If no cache hits, a miss is returned (in this design there is no L3 of caches) Figure 4.1 display the AMD multi-core architecture. But as we know in case of the multi-core simulator, shared caches must be checked whether the variables have been changed by another core or not. Further actions depend on the fact whether the requested data are already cached or not. This will be done by (ESI) cache coherence protocol.

In our multi-core architecture the embedded DPCAM behaves as an internal register file.

At the same time it is considered as shared L2 of caches.

Figure 4.1: AMD Multi-core Architecture [AMD07]

The ESI cache coherence protocol can be abandoned in our design because any core modifies variable can broadcast it to all DPCAM caches in its row. So, any shared variable is up to date for all caches. So, the state is either valid or invalid. In other word all the valid variables in caches is a shared at all time. Figure 4.2 display the Embedded DPCAM multicore architecture.

AMD Vallgrind simulator has two caches. One first level of cache and one second level shared cache for each core; each of them has instruction and data. So there is various numbers of caches dependent on the number of cores. This simulator implements an algorithm to generate these caches by using a one dimensional array of caches for each cache level. The maximum number of caches is assigned by the parameter multi-core in simulator, in this simulator there is a maximum eight cores.

In Embedded DPCAM simulator there are also two levels of caches. The first level of cache for each core and the shared second level of cache had been put at crossbars. in second level of cache the number of caches equal the square of number of cores  $n^2$  where n is the number of cores, this can be done by using a two dimensional array of MPCAM (which is explained in chapter 3), the size of array is assigned by the parameter multi-core number in simulator, then any OF for all cores want to search data, read the column of MPCAM simultaneously and any SB of all cores want to write data broadcast data to row of MPCAM simultaneously. The interconnection networks between cores represents the main differences between AMD and our model, where in AMD used crossbar switch interconnection networks while in our model we used crossbar embedded DPCAM as new design of interconnection networks.

Figure 4.2: Crossbar Embedded DPCAM Multi-core Architecture

#### 4.2 Results

In this section we will handle the results that have been obtained by the valgrind simulator. This results help use to compare between the AMD multi-core and our proposed multi-core system. Many benchmarking program used to test multi-core system, by using this program we can study the behaviour of our proposed system with AMD multi-core. This includes studying the five parameters listed in section 2.2.3.

#### 4.2.1 Benchmarking program